# Distribution System Protection with Resistive Type SFCL during Intense Fault Conditions

Rupali U. Pawar1<sup>1</sup>, Pranita Chavan<sup>2</sup>

<sup>1</sup>(Department of Electrical engineering, Y.T.I.E.T/ Mumbai University, India) <sup>2</sup>(Departmentof electrical Engineering, HOC Pillais /Mumbai University,India) Corresponding Author: Rupali U. Pawar1

**Abstract :** In this paper, a modified SFCL with extended resistance values for reduce the fault currents magnitude in the grid system was proposed. With the expansion in the benchmark estimation of the SFCL, the current is additionally reduced when contrasted with ordinary SFCL. The decreased values are looked at in this paper which represents the effectiveness of the proposed SFCL. Because of micro grid association with the power network, extreme current is a significant issue, to be explained for effective execution of micro grids. In any case, a deficiency of research concerning the area of SFCL in grid is felt. In this work, a resistive sort SFCL demonstrate was actualized by utilizing Simulink in Matlab as a stage. The outlined SFCL model could be effectively used for deciding an impedance level of SFCL as indicated by fault current of different sorts of grid. Additionally, grid transmission and distribution with network was displayed to decide the areaand the performance of the SFCL. The SFCL is introduced in IEEE 6 bus system with fault at different locations and observe the difference of fault current.

Keywords: Matlab, Micro grid, SFCL (Superconducting Fault Current Limiter), Simulink, SimPowersystems.

\_\_\_\_\_

Date of Submission: 28-09-2017

Date of acceptance: 10-10-2017

#### I. INTRODUCTION

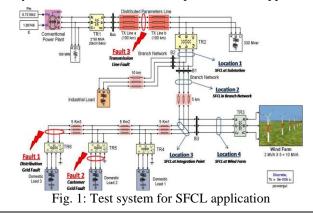

Now days, there is increase in the electrical network to satisfy the energy demand with the help of not only conventional sources but also distributed generation. Due to consumption of electrical energy and increment in demand energy leads to increase in the system fault levels and it crosses the rated capacity of the existing circuit breakers. To increase the installed electrical power, interconnection of electrical transport network is carried out. At interconnection it might prompt short circuit currents of high. The fault current will increment past the rating of the current defensive parts in the system. In this way, to stay away from the short circuit current utilization of a device is presented [1]. These are known as Fault Current Limiters (FCLs). The FCLs are comprised of superconducting materials on the grounds that superconducting materials have an exceedingly non-straight conduct which is perfect for the application as FCLs. These FCLs have capacity to make electrical system successful by currents and result in significant sparing in the speculation of high limit circuit breakers. In this paper a resistive superconducting shortcoming current limiter (RSFCL) proposed, to decrease the current and to beat the downside in the power system by putting or introducing SFCL system. Which improves stability of system. Superconducting Fault Current Limiter (SFCL) is one of the most novel alternate solutions to avoid the problem of increasing fault current. It improves power system reliability and stability by reducing the fault current instantaneously [2]. SFCLs have expansive impedance at fault conditions and have low impedance in typical conditions and furthermore recovery to zero impedance. Superconducting materials have an exceptionally non-direct conduct which is perfect for the application as FCLs.

Superconducting Fault Current Limiter (SFCL) have capacity to overcome and suppression of fault current issues with numerous points. There are different sorts of SFCLs, which can be ordered in three sorts, for example, the resistive sort, the inductive sort and bridge type SFCL. All the more particularly, the present restricting conduct relies upon their nonlinear reaction to temperature, current etc. Expanding any of these parameters can cause a change between the superconducting and the ordinary regime [3]. A Superconducting current limiter responds quickly, resets itself and has negligible effect on system execution at normal operation.

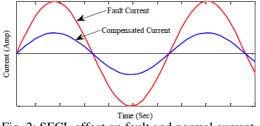

Fig. 2: SFCL effect on fault and normal current

### II. MODELLING OF SFCL

In this fault current limiters are comprised of superconducting materials. The protection of the superconducting component is basically zero, hence at ordinary working of system, it works with no restrictions and it is conceivable to limit impedance. Assume any fault in system, fault current achieves ordinarily rated, yet because of the superconducting component it returns quickly to its ordinary state. This is on the grounds that the expanded in protection/impedance which constrains fault current to a level. At typical operation the present coursing through the superconducting component disperses low energy [4]. The losses because of the fast bring up in protection warms the superconductor over the basic temperature and the superconductor protection changes its state from superconducting to Normal state and fault current is diminished quickly. This is called extinguish of superconductors. At the point when fault current has been decreased, the protection component recover its superconducting state.

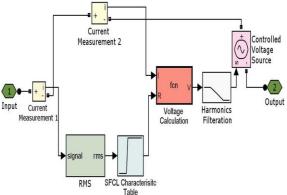

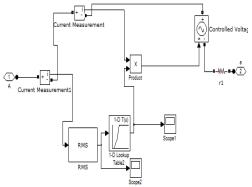

The parameters used to design such model are as: (i) Transition or response time = 2ms, (ii) maximum impedance =  $20\Omega$ , (iii) minimum impedance =  $0.01\Omega$ , (iv) Recovery time = 10ms and (v) Triggering current = 550 Amp. Fig. 3 demonstrates the Resistive SFCL, in which RMS square is utilized to compute the RMS value of approaching current which at that point sustained to subsystem of SFCL table piece. The SFCL table is utilized to choose whether the impedance level goes high or low.

Fig. 3: Modeling of SFCL in Simulink

The examination shows the estimation of protection of SFCL as: (an) if the approaching current is underneath the activating current level, and afterward the SFCL protection is least. (b) if the approaching current is over the activating quality, at that point its protection is greatest near the impedance level. The switch block is utilized to set the estimation of impedance to least or most extreme. After SFCL subsystem there is filter block and controlled voltage source square. These are utilized to decrease harmonics and to compensate voltage sag separately.

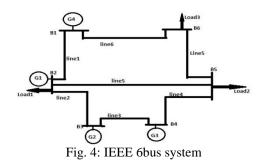

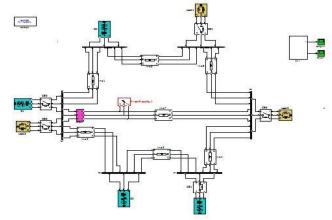

## III. IEEE 6 BUS SYSTEM

The line diagram is as below:

As it can be seen that the 6 bus system contains three ordinary sources with a voltage of 11kV, 50 Hz supply. The transmission lines considered are medium transmission line with three phase ' $\pi$ ' section lines.With the high value of loads the voltage of the buses drops due to the demand of high reactive power from the sources [5]. This power can be compensed with enhancement of dynamic power associated at any rate.The ratings of all the elements in the 6-bus system is given below:

| Table I: Load Data |               |                        |  |  |

|--------------------|---------------|------------------------|--|--|

| Bus                | Real Power,MW | Reactive<br>Power,MVAR |  |  |

| At Bus2            | 20            | 10                     |  |  |

| At Bus5            | 40            | 15                     |  |  |

| At Bus6            | 30            | 10                     |  |  |

| Table II: Line Data |      |                   |                   |  |

|---------------------|------|-------------------|-------------------|--|

| Line                | Bus  | Positive Sequence | Positive Sequence |  |

| No                  | Code | Resistance,p.u    | Reactance, p.u    |  |

|                     | p-q  |                   |                   |  |

| 1                   | 1-2  | 0.05              | 0.20              |  |

| 2                   | 2-3  | 0.10              | 0.50              |  |

| 3                   | 3-4  | 0.20              | 0.80              |  |

| 4                   | 4-5  | 0.10              | 0.30              |  |

| 5                   | 5-6  | 0.20              | 0.40              |  |

| 6                   | 6-1  | 0.10              | 0.15              |  |

| 7                   | 2-5  | 0.20              | 0.50              |  |

| Table III. | Concreter | Data |

|------------|-----------|------|

| Table III: Generator Data |           |        |     |          |

|---------------------------|-----------|--------|-----|----------|

| Generator No              | P+jQ p.u. | V p.u. | MVA | Bus Type |

| G1                        | 0+j0      | 1.00   | 100 | Slack    |

| G2                        | 0.1+j0.05 | 1.041  | 15  | PV       |

| G3                        | 0.3+j0.2  | 1.0190 | 40  | PV       |

| G4                        | 0.2+j0.1  | 1.071  | 30  | PV       |

## IV. SIMULATION RESULTS AND OUTPUTS

Fig. 5: Simulink model of IEEE 6 bus with SFCL

The test system is considered with four three phase sources with three loads at different buses with a fault at Bus 2.

Fig. 6: SFCL module internal modeling

The SFCL model has a characteristics table which finalizes the output resistance with respect to the input rms current value.

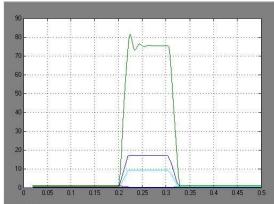

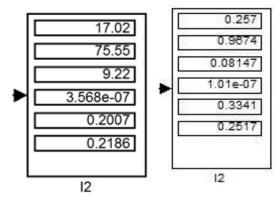

Fig. 7: Bus currents of IEEE 6-bus without SFCL

The fault current without SFCL is observed to be 75.55Ampere.

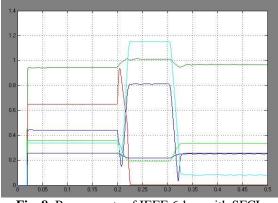

Fig. 8: Bus currents of IEEE 6-bus with SFCL

The fault current with SFCL is observed to be 0.98Ampere.

Fig. 9: Current magnitude comparison of 6buses with and without SFCL

| Liı | ne | Without | With | Percentage | Effect    |

|-----|----|---------|------|------------|-----------|

|     |    | SFCL    | SFCL | Reduction  |           |

| 7   |    | 75.55   | 0.98 | 98.70      | Decreased |

| 1   |    | 17      | 0.8  | 94         | Decreased |

| 2   |    | 9       | 1.1  | 87.1       | Decreased |

|     |    |         |      |            |           |

Fig 10: Fault on bus2 with SFCL

## V. CONCLUSION

With the above graphical representations of currents at each bus during fault condition on bus 2 in IEEE 6bus system with fault time of 0.2-0.3sec with and without SFCL it can be clearly observed that the current at the bus 2 with SFCL is suppressed during fault. The value of the current magnitude is decreased from 75.4Amp to 0.98Amp during fault. Analysis can be continued with different locations of fault and SFCL and comparison tables.

#### REFERENCES

- Lin Ye, LiangZhen Lin and Klaus-Peter Juengst, "Application Studies of Superconducting Fault CurrentLimiters in Electric Power Systems", IEEE Transactions on Applied Superconductivity, vol. 12, no. 1, MARCH 2002.

- [2]. Lin Ye, M. Majoros, T. Coombs and A. M. Campbell, "System Studies of the Superconducting Fault Current Limiter in Electrical Distribution Grids", IEEE Transactions on Applied Superconductivity, vol. 17, no. 2, JUNE 2007.

- [3]. ByungChul Sung, Dong Keun Park, Jung-Wook Park and Tae KukKo, "Study on a Series Resistive SFCL to Improve Power System Transient Stability: Modeling, Simulation and Experimental Verification", IEEE Transactions On Industrial Electronics, vol. 56, no. 7, JULY 2009.

- L. Dessaint, K. Al-Haddad, H. Le-Huy, G. Sybille, and P. Brunelle, "A power system tool based on Simulink," IEEE Trans. Industrial Electron., vol. 46, no. 6, pp. 1252–1254, Dec. 1999.

K. Maki, S. Repo, and P. Jarventausta, "Effect of wind power based distributed generation on protection of distribution network," in

- [5]. K. Maki, S. Repo, and P. Jarventausta, "Effect of wind power based distributed generation on protection of distribution network," in IEEE Developments in Power System Protection, Dec. 2004, vol. 1, pp. 327–330.

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) is UGC approved Journal with Sl. No. 4198, Journal no. 45125. Rupali U. Pawar1. "Distribution System Protection with Resistive Type SFCL during Intense Fault Conditions." IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE), vol.

12, no. 5, 2017, pp. 16–20.